近日,华中科技大学叶大蔚课题组在固态电路领域国际顶级期刊《IEEE Journal of Solid-State Circuits》(简称JSSC)上发表了题为“Analysis and Design of a Series-Resonance VCO With Magnetic Mutual Resistance”的研究论文。该成果曾首发于芯片设计领域顶级会议2025 IEEE VLSI Symposium,该工作发表后受到了学术界与工业界的广泛关注,随后受邀投稿至JSSC特刊用于以长文形式详述其核心理论、设计方法与实验验证, 目前已顺利获得接收。这也是我院首个同时在VLSI和JSSC上进行发表的工作。

核心创新

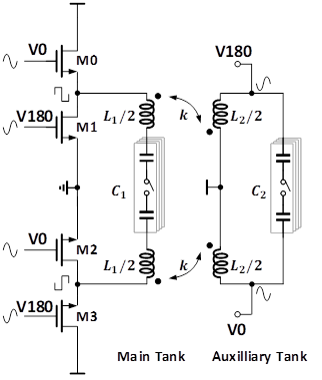

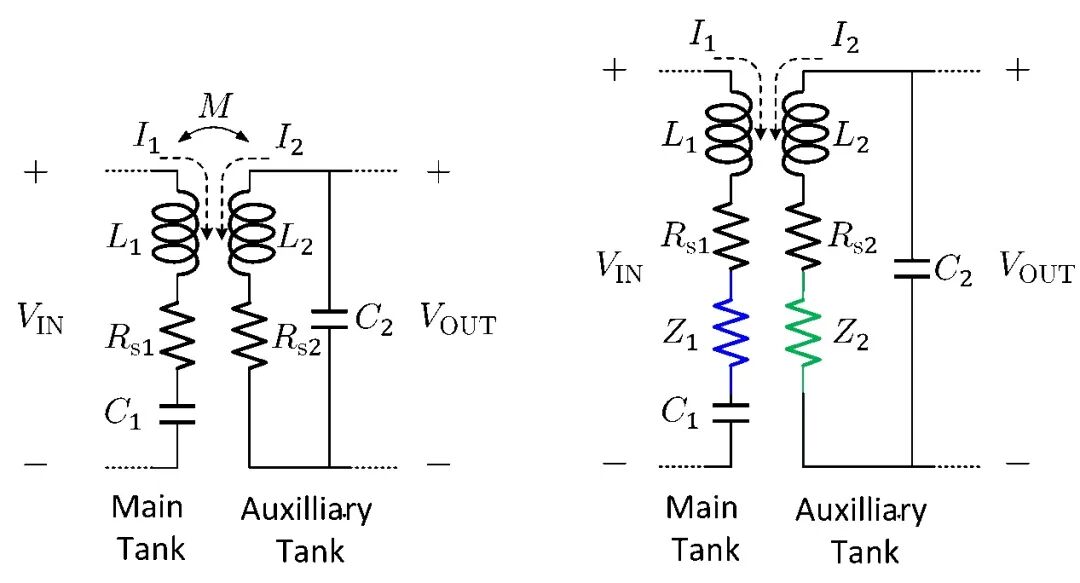

毫米波频段频率生成的频谱纯度一直是5G及未来通信系统的技术难点。针对毫米波频段压控振荡器(VCO)在低相位噪声、低功耗及紧凑面积之间难以平衡的挑战,论文提出了一种基于磁互阻(MMR)的新型串联谐振VCO(SR-VCO)架构(图1)。传统设计若想提高谐振腔阻抗以降低功耗,通常需要增加电感或电阻,但这会不可避免地损耗能量并降低Q值从而恶化相位噪声。论文提出利用单变压器的原边和副边耦合,通过控制电流之间 90° 的相位偏移,在谐振腔中产生两个等效电阻(即MMR,图2)。这种电阻是由磁耦合产生的,它既能显著增强谐振腔的等效阻抗(从而降低核心电流和功耗),又不会像实物电阻那样产生热噪声并损耗Q值。基于该原理设计的SR-VCO具有以下几点优势:

· 功耗降低: MMR增大了谐振腔阻抗,在不降低Q值的前提下,显著降低了核心功耗,相较于传统串联谐振振荡器降低约1个数量级。

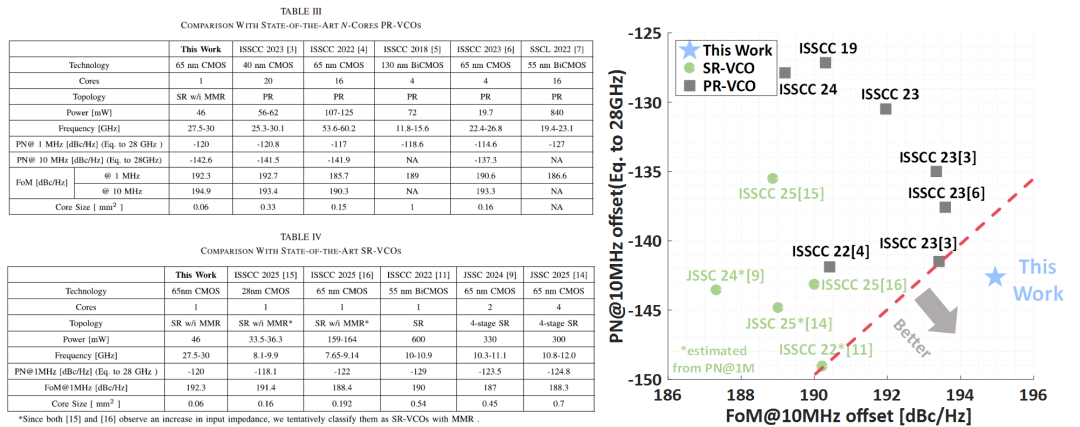

· 低相位噪声: 论文深入分析了磁互电阻对脉冲敏感函数(ISF)的影响,通过降低ISF幅度,MMR有效抑制了有源器件噪声,实现了极低的相位噪声性能,在27.78GHz频率处达到了-120.09 dBc/Hz (@1MHz offset),达到国际领先水平(图5)

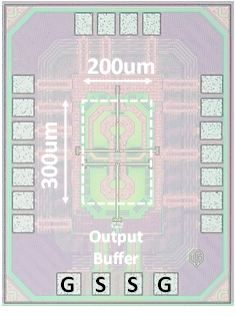

· 高集成度: 由于仅采用一个变压器,该结构相比于其他多核振荡器面积显著降低(仅0.06mm²,图3),同时达到了相当或者更优的相位噪声性能。

图1:SR-VCO电路架构图展示了利用单变压器实现的磁互电阻串联谐振腔结构

图2:变压器电路以及90°电流相移情况下的等效电路

图3:芯片显微照片

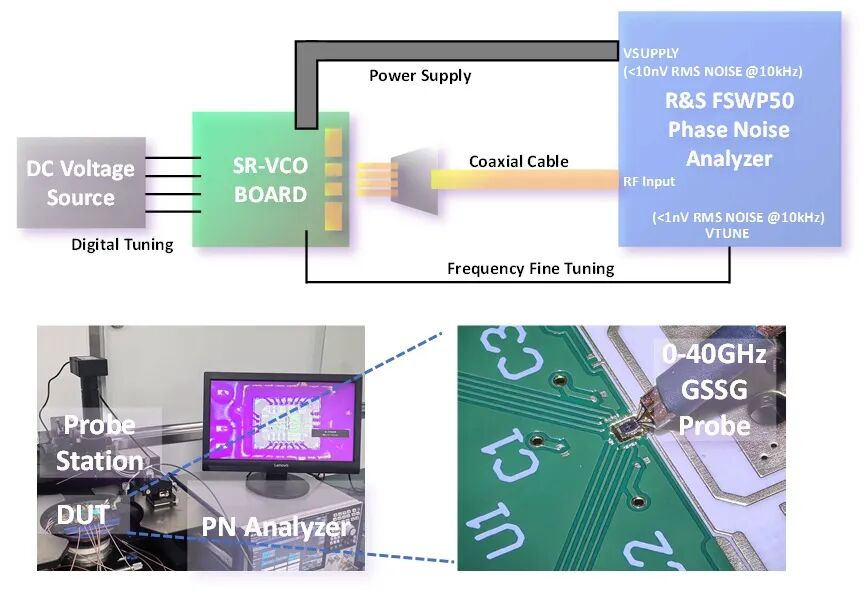

图4:测试环境

图5:性能对比表以及对比图

团队简介

本论文的第一作者为博士一年级学生陈路阳,通信作者为叶大蔚研究员。叶大蔚团队的研究方向涵盖射频/模拟前端、锁相环、频率生成电路及脑机接口电路等。陈路阳同学自2024年加入实验室以来,一直专注于毫米波频率生成芯片设计方向,并于加入课题组一年内,在芯片设计领域顶级会议2025 VLSI Symposium及顶级期刊JSSC上分别发表1篇论文。

该成果获得了国自然面上项目(62374066)和深圳市重大科技项目(KJZD20240903103159001)的支持。