为推动小芯片创新的下一波浪潮,Cadence 成功流片其第三代通用小芯片互连技术(UCIe)IP 解决方案,在台积电先进的 N3P 工艺上实现了业界领先的每通道 64Gbps 速率。随着行业向日益复杂的 AI、高性能计算(HPC)和数据中心架构发展,对强大、高带宽的芯片小芯片互连的需求从未如此迫切。这一里程碑式的成就使 Cadence 处于领先地位,能为要求最严苛的应用打造可扩展、高能效的多芯片系统。

随着制程节点推进到 3 纳米及以下,系统级芯片 (SoC) 设计人员面临着一项挑战:需在优化功耗、性能和面积 (PPA) 的同时,满足高速、可靠的芯片间通信需求。Cadence UCIe IP 解决方案完全符合 UCIe 规范,其设计初衷就是直接应对这些挑战。该方案借助台积电创新的 N3P 技术,实现了出色的能效表现,助力客户在不牺牲性能的前提下达成严苛的能耗指标。

基于台积电 N3P 工艺的64Gbps UCIe IP 子系统流片

Cadence UCIe IP 实现 64G 速率流片,标志着小芯片互连技术取得了重大突破。该方案支持每通道高达 64Gbps 的速率,设计人员可实现超高带宽密度,为可扩展的小芯片架构开辟新的可能性。其灵活且无缝地整合各类现有接口协议,例如 AXI、CXS.B、CHI-C2C、PCIe 和 CXL,可快速集成到各种平台中,包括 AI 加速器、网络设备和先进的数据中心系统。

可靠性和集成灵活性是 Cadence UCIe IP 的核心优势。先进的纠错、通道裕量和诊断功能,确保其在异构多芯片环境中稳定运行。该架构的设计旨在简化系统集成,支持多厂商芯片生态系统间的无缝互操作性。

“自 2018 年首次流片以来,Cadence 便一直处于芯片间互连解决方案的最前沿。2022 年转向 UCIe 技术后,过去两年我们充分展示了第一代和第二代 UCIe 解决方案的硅片验证成果,”Cadence 硅解决方案集团市场营销副总裁 Arif Khan 表示。“鉴于 AI 和高性能计算应用对吞吐量和效率的巨大需求,我们很自豪能够推出速率可达 64G 的第三代 UCIe IP。通过与我们值得信赖的合作伙伴台积电合作,我们正在为双方的客户带来高质量、高效的解决方案。”

面向 AI /高性能计算应用的业界领先特性

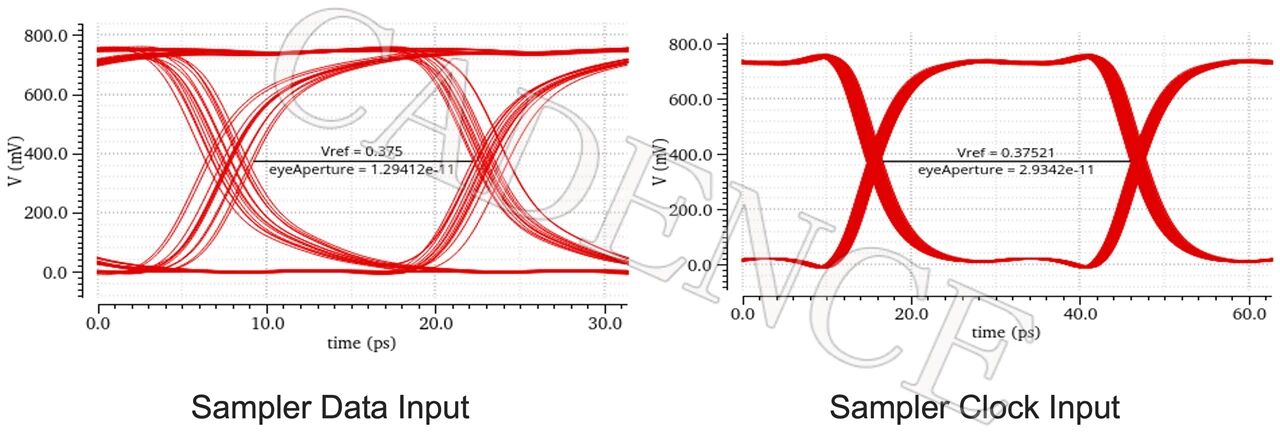

该解决方案可提供 64Gbps 的传输性能,在标准封装中实现了 3.6Tbps/mm 的出色带宽密度,在先进封装中更是达到 21.08Tbps/mm。凭借业界一流的 PPA(性能、功耗和面积)指标,该架构针对高性能计算 (HPC) 和人工智能 (AI) 应用进行了优化。与所有 Cadence UCIe 系列产品一样,它支持多种协议,包括 AXI、CXS、CHI-C2C、PCIe 和CXL.io,并与高速 PHY 无缝集成,提供完整的 IP 子系统,从而加速设计部署进程。自校准功能和基于硬件的启动无需固件干预,可实现快速系统初始化并简化设置。简化的时钟方案和集成的锁相环 (PLL),结合在电压和温度变化范围内的稳定性能,确保了可靠性和效率,使设计人员能够专注于核心逻辑这一关键环节。

凭借这一成果,Cadence 丰富了其全面的 IP 产品组合,为客户和合作伙伴提供了攻克现代计算挑战所需的工具。通过融合更高的数据速率、全面完善的客户解决方案以及严格的标准合规性,Cadence 正在助力下一代可扩展、高性能的系统。

点击了解更多关于 Cadence 的 UCIe IP 解决方案以及它如何加速您的下一代设计。