30000人次观看!这个数据创下了集微开讲的直播新记录。

3月28日20点,厦门云天半导体创始人于博士做客“集微直播间·开讲”第三期,开讲《晶圆级三维封装技术进展》。话题的火爆,内容的翔实,加之于博士的精彩讲解,使得本期集微开讲在全网得到了超高的关注度。

“集微直播间·开讲”也是集微直播间上线以来,继“集微龙门阵”“芯力量·芯创路演”“连线”后推出的又一档重磅栏目。以“大咖私享”形式,每期邀请顶级大咖作为演讲嘉宾,就时下行业热点话题进行深入分享和探讨。

厦门云天半导体创始人于大全博士

晶圆级封装成为主角

“封装技术开始仅仅是起支撑作用的配角,由于时代的演进,现在走向了舞台中心。”

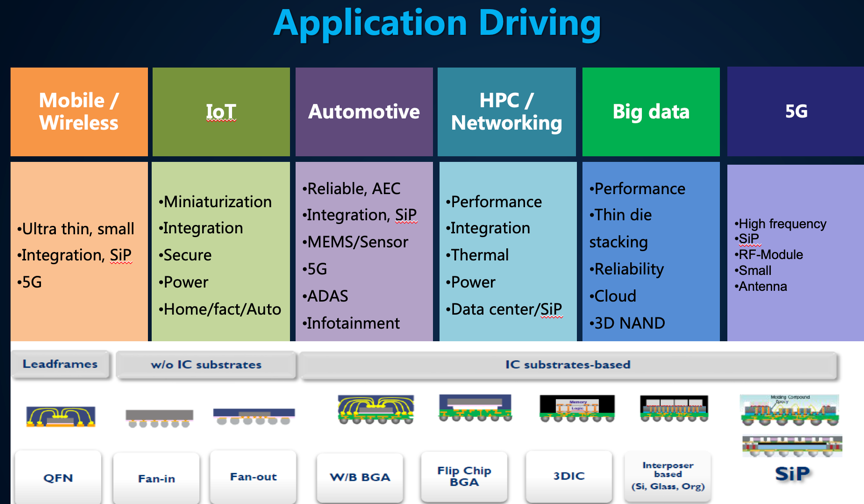

对于这个论断,于博士给出了两个理由。第一是摩尔定律趋近极限,以晶圆级封装为代表的先进封装已经成为维系其发展的引擎。第二是半导体产品进入碎片化和多元化的应用驱动时代,不再以智能手机为单一驱动力,而是逐渐走向AIoT、智能驾驶、5G等多应用驱动的局面,对封装技术的要求越来越高。

回顾先进封装的发展历程,本世纪初是爆发的原点,大量新型封装技术开始出现,包括晶圆级封装(WLP,Wafer Level Package), Fan-Out, 3D WLCSP, 2.5D, 3DIC, 3D FO等等,人们开始在晶圆表面进行布线和互联,提高了芯片封装密度和散热效果。在进入2010年以后, WLP、硅通孔技术(TSV,Through Silicon Via)、2.5D Interposer、3D IC、Fan-Out 等技术全面产业化,推动了先进封装技术的快速发展。“重要的表现就是,从线宽互连能力上看,过去50年,封装技术将线宽从1000µm提高到1µm,甚至亚µm级”于博士强调。

据于博士介绍,主流的先进封装技术平台,包括Flip-Chip,WLCSP,Fan-Out,Embedded IC,3D WLCSP,3D IC,2.5D interposer,大部分和晶圆级封装技术相关。因为晶圆厂的参与,如台积电和Intel等,晶圆级封装技术本身不断创新发展,以应对更加复杂的三维集成需求。

封装技术的核心就是互联技术,从最初的引线技术,发展到芯片倒装(Flip Chip),再到现在的TSV技术,本质就是从点互联到面互联再到垂直互联的发展过程。当前,高密度TSV技术/Fan-Out(扇出技术)由于其灵活、高密度、适于系统集成的特质,已经成为目前先进封装的核心技术。

环顾整个产业发展,我国的封装技术已经有了长足的进展,长电和华天已经接近世界顶尖水平。但是,存在的问题也比较明显。于博士指出了两点:一是高密度Fan-Out/2.5D/3D IC等高端晶圆级器件集成技术未实现规模化量产,二是拥有自主知识产权的新技术尚未成为先进主流封测技术。

无所不在的TSV

广义上讲,在同一个封装体内于垂直方向叠放两个以上芯片就被称为3D IC,其核心就是TSV技术。

TSV技术运用晶圆的薄化、钻孔、以导电材质填孔、晶圆连接等,将逻辑、内存及模拟组件进行整合,其运作方式类似于SoC (Systen on Chip),却又能克服SoC 所面临的瓶颈。由于连接线位于芯片之间,使得内部连接路径更短,可使得芯片间的传输速度提升、噪声减小并提升整体的效能,同时可达高密度要求。于博士认为,采用TSV集成,可以提高系统集成密度,方便实现系统级的异质集成。

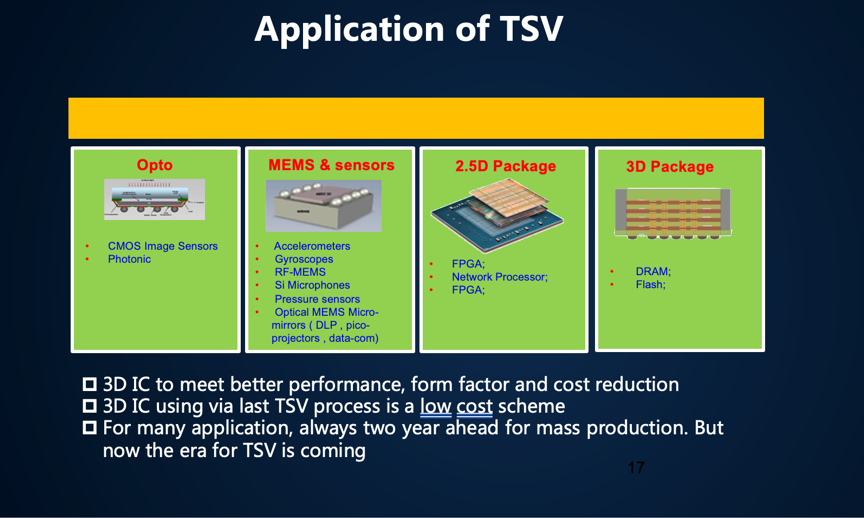

在TSV的基础上,演化出了3D WLCSP,3D IC,2.5D interposer等主流封装平台。目前,运用TSV技术的芯片已经在四个领域大幅出货,其中包括CMOS图像传感器、MEMS、FPGA和DRAM/Flash。

据于博士介绍,台积电2010年开展2.5D TSV转接板,即CoWoS技术研发,采用65nm工艺,线宽可以达到0.25µm,实现4层布线,为FPGA和GPU等高性能产品的集成提供解决方案。

Xilinx(赛灵思)的Virtex-7 2000T是最具代表性的产品之一。基于2.5D转接板技术将四个不同的28nm工艺的FPGA芯片集合在一起,构建了相当于容量达2000万门ASIC的可编程逻辑器件。

HBM(High Bandwidth Memory,高带宽存储器)是TSV在存储领域应用的典范。通过细节距、高密度TSV转接板,多个DDR芯片堆叠在一起后和GPU封装在一起,实现大容量,高位宽的DDR组合阵列。AMD Radeon Vega GPU中使用的HBM2(最新的HBM),由8个8Gb 芯片和一个逻辑芯片通过TSV和微凸点垂直互连,每个芯片内就包含了5000个TSV通孔。

Intel公司也有类似的技术,在2020年发布的Lakefield处理器中,10nm计算芯片与22nm基底芯片之间使用TSV通孔做电气互联,同时计算芯片之间的通信则通过基底芯片中的互联来完成。

台积电的SoIC将3D IC推向新高度。这是在CoWoS(Chip on wafer on Substrate)与多晶圆堆叠(WoW)的基础上开发出的封装技术,应用于10nm及以下的先进制程进行晶圆级的键合。SoIC技术核心依旧是TSV,可以达到无凸起的键合结构,可以把很多不同性质的临近芯片整合在一起。

扇出封装、TGV和3D WLCSP

扇出封装的发展要得益于苹果iPhone 7系列手机的A10处理器。因为苹果和台积电的强强联手,使得这项技术迎来了发展的春天。

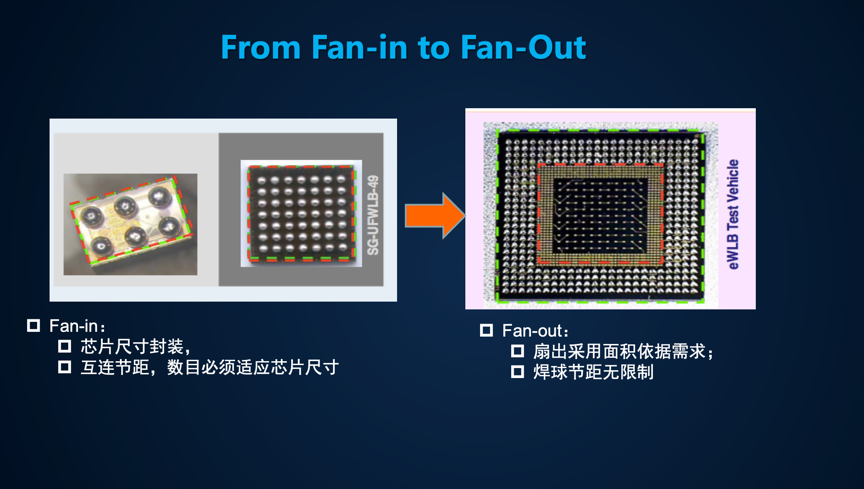

扇出封装是扇入封装(Fan-in)的改进。其采取拉线出来的方式,可以让多种不同裸晶,做成像WLP(Wafer Level BGA)工艺一样埋进去。假设放置多颗裸晶,可以省却多层封装,从而降低了封装尺寸和成本。

扇出封装可以替代绝大部分使用传统封装的产品。但是,这个巨大的市场被台积电这样的晶圆厂所把持。于博士认为,对于初创的封装厂来说,要选择扇出封装,如果不能在成本和技术上做到兼备,就无法获得市场认可。

台积电的Info封装是扇出封装的代表,通过将芯片埋入模塑料,以铜柱实现三维封装互连,为AP制造和封装提供了整体解决方案。Info封装让台积电获得了巨大的成功,风光的背后却是在良率很低状况下的长时间持续投入,这是大部分封装厂难以做到的。

值得一提的是,华天科技也在2015年开始扇出封装技术开发,开发出了独有的埋入硅基板扇出型封装技术eSiFO®(embedded Silicon Fan-out)。该技术具有可以实现多芯片系统集成SiP,易于实现芯片异质集成等特性,已经应用在RF Transceivers、Controller、Sensors、4G射频前端、毫米波芯片,FPGA等产品中。

扇出封装的一个最新分支是扇出型面板级封装(Fan-Out Panel Level Packaging,FOPLP)。三星电机(Samsung Electro Mechanics ,SEMCO) 过去两年投入4亿美金研发面板级封装,第一个实现量产。行业中有种观点认为该封装会成行业大趋势。于博士对此持谨慎的态度,“具有面板技术基础,具有大芯片集成需求客户才是发展面板级封装研发和产业化的基础。”

先进封装技术的发展一直与材料的开发使用密不可分。近年来,TGV(玻璃通孔集成)技术由于创新性的低成本通孔加工技术开发成功,在封装领域大放异彩。与硅相比,玻璃的介电常数较低,电阻率较高,因而具有较好的高频性能,在射频传输方面有更大的优势。但是,TGV的最大难点在于玻璃上穿孔和填充,这个问题困扰了业界很多年。好消息是,于博士领导的团队采用了激光诱导刻蚀的方法,已经初步形成了一个低成本的解决方案。“尽管在高密度转接板上还有很长的路要走,但在一些低端产品(IPD)上已具备量产能力了。“

3D WLCSP技术出现伊始,就被业界看好,其完全符合消费电子发展的需求和趋势(产品的轻小短薄化和低价化),现在供不应求的CIS芯片就大量应用了该封装。在射频领域,滤波器和SAW同样大量采用了WLCSP封装。随着封装技术向着系统集成、高速、高频、三维、超细节距互连方向发展,3D WLCSP将成为多方争夺焦点。

由于摩尔定律已经趋于极限,晶圆厂不惜重金研发封装技术来增强竞争力。对于未来的技术发展,晶圆厂会取代封装厂成为引领者吗?于博士对此给出了肯定的答复。不过,他也认为,随着芯片封装需求的多样化,封装厂依然有自己不可替代的位置。将来的行业格局,一定是百花齐放,合作共赢的局面。

集微直播间将推出全新直播专栏——“集微公开课”,联合行业头部企业,共同打造行业内最专业、优质的在线培训课程,深化产教融合,助力中国ICT产业发展。

第一期“集微公开课”邀请到了北京兆易创新科技股份有限公司产品市场总监 金光一先生,带来以《GD32 MCU:持续打造物联网智慧开发平台》为主题的精彩演讲。本期集微公开课将于3月31日(周二)晚上20:00直播,参与直播活动还有机会获得基于Cortex-M23内核的E230系列开发板和精美礼品,数量有限,快来点此报名!

(校对/Yuna)

登录

登录