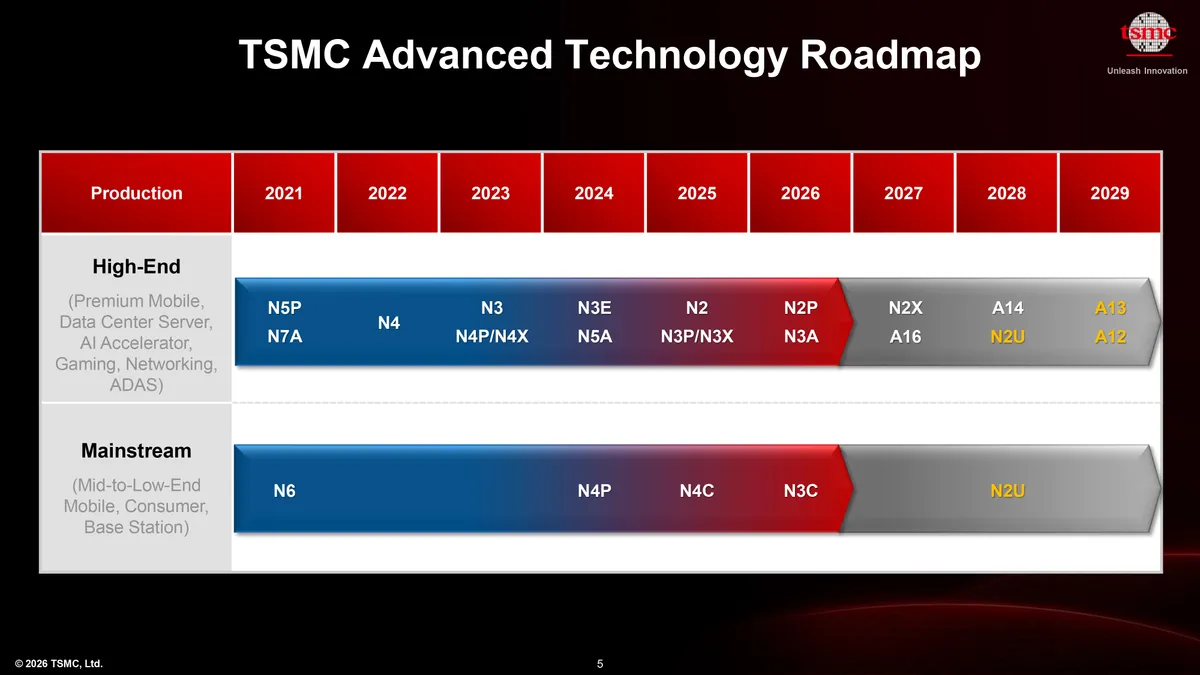

台积电(TSMC)周三(4月22日)在其2026年北美技术研讨会上公布了截至2029年的通用制造技术路线图。此次发布的重点包括:1.2nm和1.3nm级制程(分别命名为A12和A13)、对N2家族的意外延伸N2U,以及在2029年前不计划采用High-NA EUV光刻技术。或许最值得关注的是,公司进一步明确了多路径并行推进新节点开发的策略。

“去年我们发布了A14,作为最先进的第二代纳米片(nanosheet)技术,计划于2028年投产,”台积电业务发展与全球销售高级副总裁兼副COO Kevin Zhang表示。

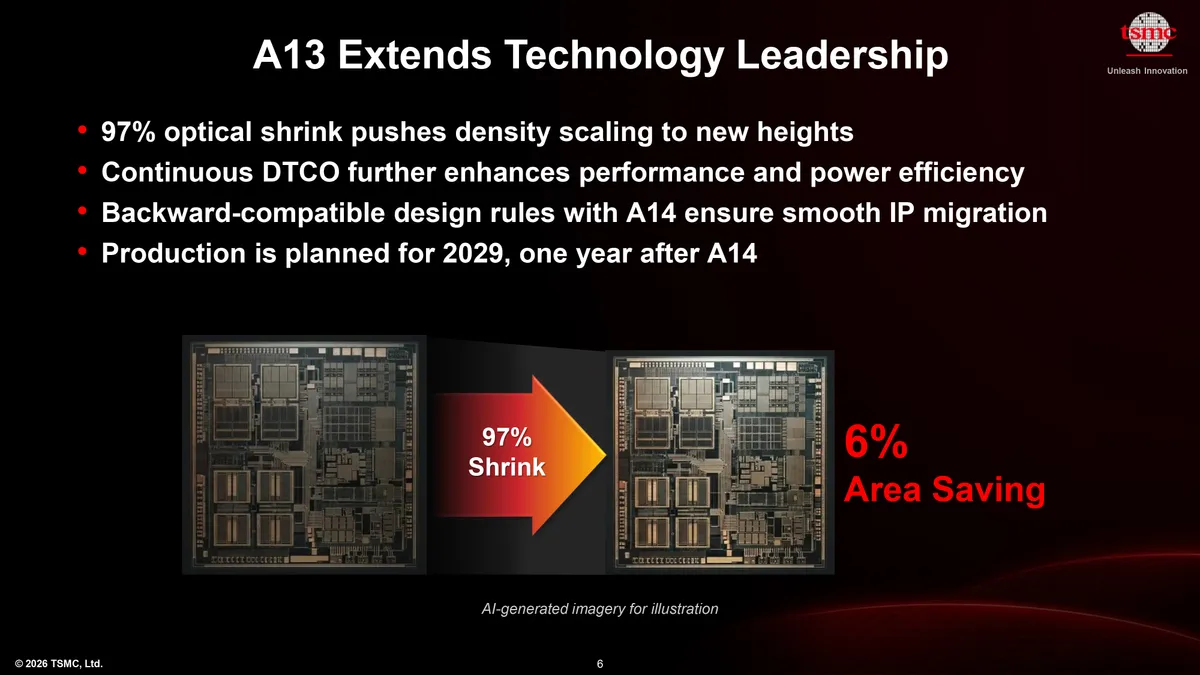

“今年我们推出了A14的衍生版本,包括A13和A12,均计划在2029年投产。A13是在A14基础上的渐进式优化,主要通过光学缩放实现,在保持完整设计规则和电气兼容性的同时,实现约6%的面积缩减,使客户仅需极少重新设计即可受益。”

改变游戏规则

历史上,台积电的大部分收入来自智能手机行业,但近年来,AI和HPC(高性能计算)已反超手机业务。这一变化清晰体现在其路线图中:台积电将先进制程按终端市场需求进行“分轨”规划,而非“一刀切”。具体来说,公司将继续每年为客户端应用推出一个新节点,同时每两年为重负载的AI和HPC应用推出一个新节点。

一方面,N2、N2P、N2U、A14、A13等制程主要面向智能手机和客户端设备——这些市场更看重成本、能效和IP复用,对设计兼容性要求高,可以接受渐进式改进,只要能保持每年一个新节点的节奏。

另一方面,A16和A12等面向AI和HPC的节点,则必须提供显著性能提升以支撑技术迁移,成本相对不那么敏感。这类节点引入了Super Power Rail(SPR)背面供电技术,以解决AI数据中心和HPC负载的供电完整性和电流输送问题,并在性能、功耗和晶体管密度方面带来实质性提升,但更新节奏为两年一次。

A13与N2U:面向客户端的新节点

去年台积电推出了A14制程,基于第二代GAA纳米片晶体管,并通过NanoFlex Pro技术提供更高设计灵活性,预计将于2028年用于高端智能手机和客户端芯片。今年发布的A13则是在A14基础上的延续。

A13是A14的“光学缩版”,以最小扰动换取额外效率提升。其线性尺寸缩小约3%(约为原来的97%),带来约6%的晶体管密度提升,同时保持与A14完全一致的设计规则和电气兼容性。从某种意义上看,这延续了台积电以往通过光学缩放优化制程的传统(如N12、N6、N4、N3P),尽管此次提升幅度相对有限。这种方式使客户可以几乎无需重新设计即可复用IP,但性能提升也相对渐进。

A14本身可在功耗、性能和密度上实现全面提升,但需要全新的工具、IP和设计方法;相比之下,A13通过DTCO(设计-技术协同优化)实现增益,无需更改设计即可获得改进,预计于2029年量产。

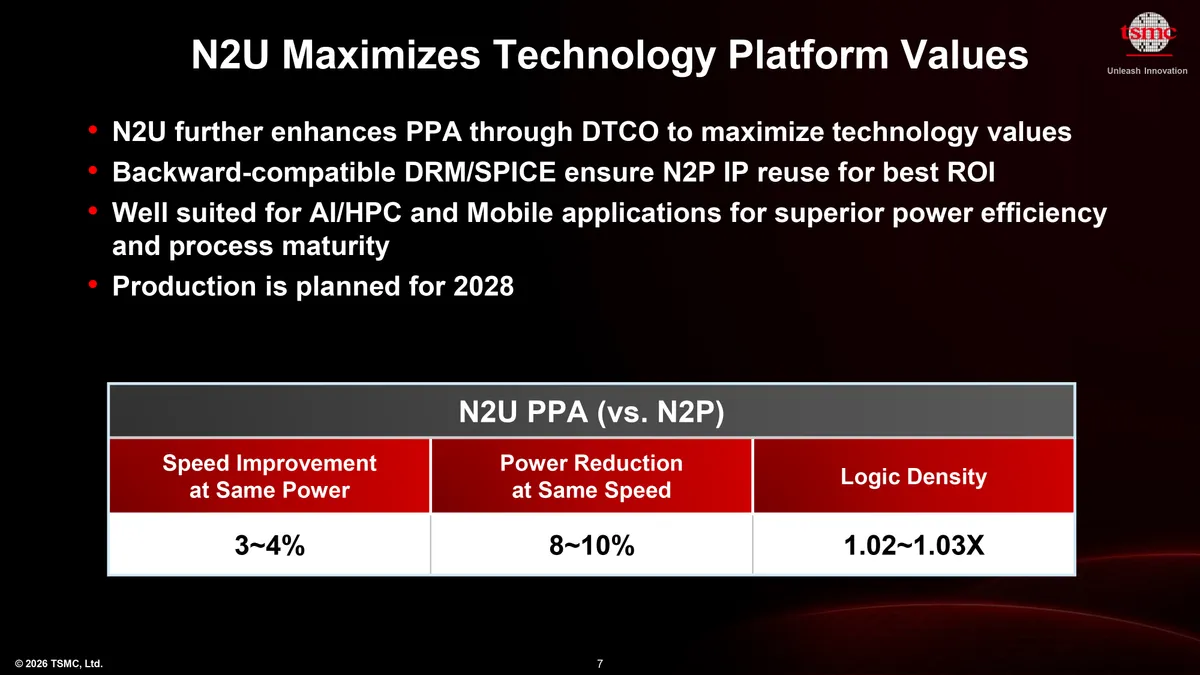

此外,台积电还将推出N2U,为客户提供低成本升级路径。N2U是N2平台的第三年延伸版本,通过DTCO可实现:同功耗下性能提升约3%–4%,或同速度下降低功耗约8%–10%,并带来约2%–3%的逻辑密度提升。该节点与N2P IP兼容,使客户无需迁移到全新制程即可开发新产品,避免高昂成本。

例如,如果某公司在2027年基于N2P开发高端产品IP,那么可以在2028年利用N2U打造中端产品。

Zhang表示:“我们通过N2U持续扩展2nm平台,通过DTCO提升性能、功耗和密度。我们的策略是在节点推出后持续优化,让客户在获得渐进式PPA收益的同时,最大化设计投资回报。”

A16、A12与N2X:不惜成本追求极致性能

虽然N2将同时用于客户端和数据中心,台积电还在推进A16,该节点引入SPR背面供电,专为高性能数据中心应用打造。本质上,A16可视为带SPR的N2P,采用第一代GAA纳米片晶体管,在性能、功耗和密度方面优于N2/N2P,但成本更高。

值得注意的是,A16目前被列为2027年节点(相较此前2026年略有延后)。

Zhang解释称:“A16将在2026年具备量产准备,但实际产品放量取决于客户,我们预计在2027年进入规模生产,因此按该时间表对齐。”

同时,A16并不会取代N2X。N2X是N2P的高性能版本,采用传统正面供电,用于将频率推至极限。

A16之后,将由A12接棒(预计2029年推出),为数据中心级节点带来完整世代升级。虽然台积电未披露具体数据,但预计A12相对A16的提升,类似于A14相对N2的跃升——其将基于第二代GAA纳米片晶体管与NanoFlex Pro技术。

“ A16是我们首个采用SPR背面供电的技术,”Zhang表示,“A12将是下一代,在正面和背面同时持续缩放,以实现整体密度提升。”

High-NA EUV暂无计划

一个值得注意的点是,台积电2029年的A13和A12制程均不需要High-NA EUV光刻设备。这与英特尔的路线形成鲜明对比,后者计划从2027–2028年的14A节点开始采用High-NA EUV。

“我对我们的研发团队感到非常惊讶,”Zhang表示,“他们不断找到在不使用High-NA的情况下推进技术缩放的方法。未来某一天可能会用到,但目前我们仍能从现有EUV中获得收益,无需转向成本极高的High-NA。”(校对/李梅)