近日,南方科技大学工学院国家示范性微电子学院潘权团队在高速通信与光电集成电路设计领域再次取得重要进展,研究成果包括:一是一款集成固有前馈均衡与击穿电压三倍器的线性调制器发射机芯片,二是一款支持多阶串扰消除与信号复用的单端接收机前端芯片。相关论文成果均发表于IEEE Journal of Solid-State Circuits(JSSC)。

两款芯片分别针对高速链路中发送端和接收端的核心瓶颈实现突破。JSSC为集成电路设计领域公认排名第一的国际顶级学术期刊,展现了团队在高速模拟/混合信号与光电芯片方向的前沿研究实力与国际影响力。

基于模拟多路复用器固有前馈均衡与击穿电压三倍器技术的56 Gbaud 7.3-Vppd线性调制器发射机

光互连已成为数据中心内部与数据中心间网络中最核心的部分之一。其高带宽、低信道损耗和抗电磁干扰的优势,较好地满足了中长距通信需求,以支持云计算和人工智能技术的快速发展。硅基光子技术因集成度高、成本相对较低,成为实现高速光互连的理想方案。然而,该技术在实际应用中面临核心挑战:其调制器需要较高的驱动电压才能有效工作,而现有驱动芯片技术在提升电压输出的同时,往往难以兼顾信号质量和系统效率,成为制约性能进一步提升的关键瓶颈。

本文提出了一种半速率线性发射机,其单片集成了2选1模拟复用器(AMUX)与用于光学调制器的线性驱动器。该AMUX利用时钟信号与半速率数据流之间的时序关系,实现了一种固有前馈均衡器(FFE)功能,该均衡器可通过调整时钟延迟被重新配置为二抽头或三抽头模式。此外,为提升输出电压摆幅和线性度,本文针对线性驱动器提出了一种名为“击穿电压(BV)三倍器”的拓扑结构。通过堆叠三个异质结双极晶体管(HBT),并利用放大后的输入信号为顶部两个HBT的基极提供偏置,使该驱动器在保持良好可靠性的同时,实现了比传统共源共栅拓扑结构大三倍的输出摆幅。

该设计基于130-nm SiGe BiCMOS工艺制造,所提出的线性驱动器可实现17.1dB的直流增益、39.1 GHz的6-dB带宽,以及在6-Vppd、1-GHz正弦波输出时1.6%的总谐波失真(THD)。完整发射机(AMUX+驱动器)在56-Gb/s NRZ模式下可实现7.3 Vppd的最大输出摆幅,当启用固有FFE功能时,在4.2 Vppd摆幅下实现了112-Gb/s PAM-4的最大数据传输速率,为下一代高速光互连系统提供了关键的技术突破。

基于多阶串扰消除与信号复用技术的112 Gb/s单端接收机前端

随着人工智能和云计算的快速发展,高速互连对更高数据吞吐率的需求不断攀升。单端高速收发机凭借更高的引脚效率和更低的奈奎斯特带宽要求,正在成为突破传输速率瓶颈的重要候选方案。然而,在高密度通道中,单端链路极易受到严重的远端串扰(FEXT) 干扰,导致信号完整性 (SI) 恶化。由于 FEXT 在较高频率下不再遵循理想的微分模型,此前的方法无法有效地将其消除。

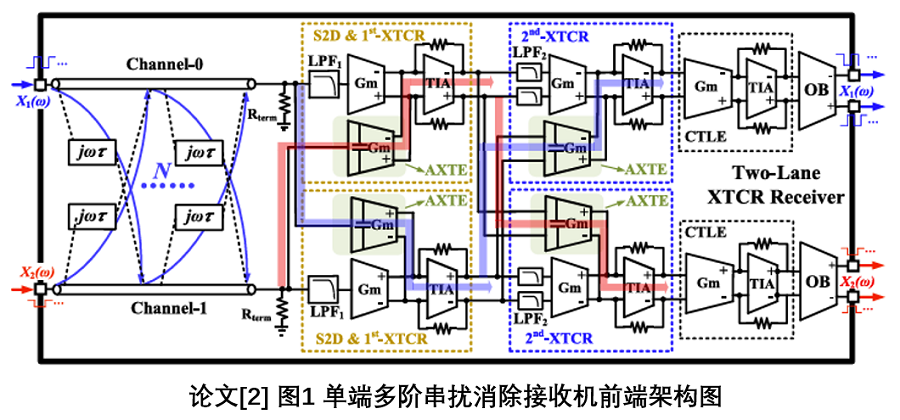

本文提出了一种采用多阶串扰消除与信号再利用技术的、用于背板链路的112-Gb/s单端PAM-4接收机前端。引入了能够准确表示较高频率下真实FEXT 的 N 阶 FEXT 模型。基于该模型,创新性地提出了一种多阶串扰消除与信号再利用技术 (M-XTCR),以最小化残余串扰并增强高频信号的再利用能力。该方案不仅能够更彻底地消除残余串扰,更能将消除过程中提取的串扰能量转化为对有用信号高频分量的主动增强,从而在抑制干扰的同时提升信号质量。

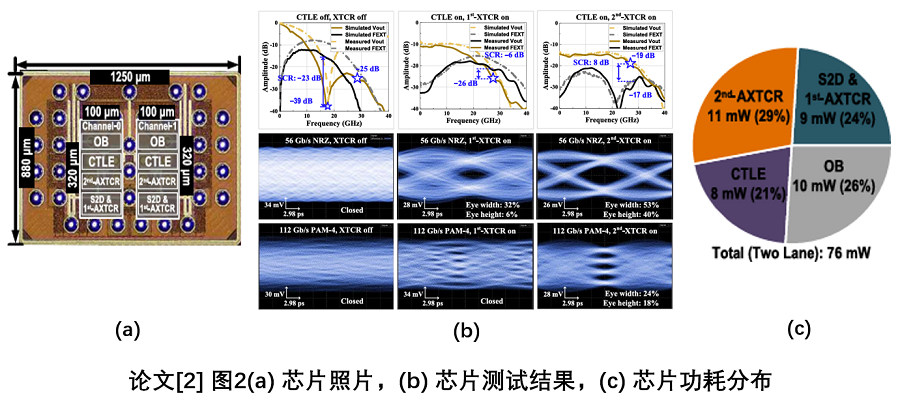

该设计基于28-nm CMOS 工艺制造,接收机前端采用二阶 XTCR 拓扑,在一个4英寸长、信串比为33-dB的信道上验证了此技术。测试结果表明,与传统一阶XTCR 相比,采用二阶 XTCR 技术的接收机前端,在 56-Gb/s NRZ 信号下,测得的水平与垂直眼图张开度分别提高了 21% 和 34%;在 112-Gb/s PAM-4 信号下,分别提高了 24% 和 18%。该设计达到了0.34 pJ/b的最佳能效,性能优于现有技术水平,为高密度单端互连系统的实用化奠定了坚实基础。

图1展示了单端多阶串扰消除接收机前端的电路架构图。图2(a),(b),(c)分别展示了提出的接收机前端芯片面积、测试结果,及其功耗分布。

钟立平为论文的第一作者。钟立平是南科大2024届博士毕业生,现为广东工业大学特聘副教授。该论文得到了国家重点研发计划、深圳市科技重大专项以及南方科技大学高层次人才科研启动基金等项目的资助。