1.介绍

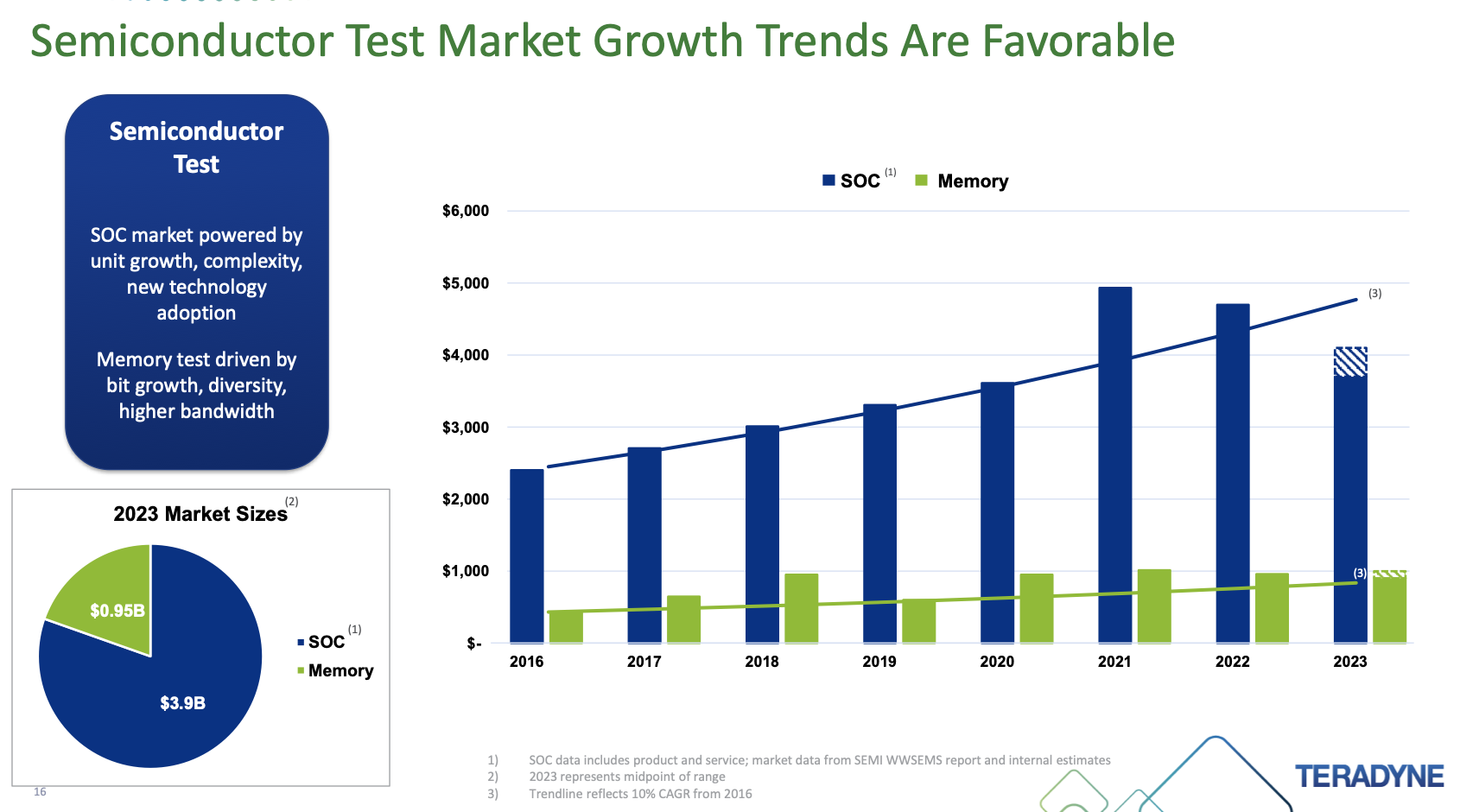

芯片封装中轻微缺陷的早期检测始终具有挑战性。传统的芯片级轻微缺陷分析工具(例如发射显微镜[1]或OBIRCH[2])不再适用于封装级分析。此外,广泛使用的成像技术(例如X射线和CSAM)在筛查轻微缺陷方面效果不佳,特别是当缺陷尺寸小于成像分辨率时。轻微缺陷通常在特定条件下表现为功能失效,例如高温、过度应力、电压偏高或长时间工作后。尽管商用芯片在各种温度下进行了广泛的功能测试,但0.2%-0.5%的残余现场回报率仍然不可避免。因此,探索对测试条件依赖性较小的芯片封装轻微缺陷更有效的早期检测方法具有极大意义。

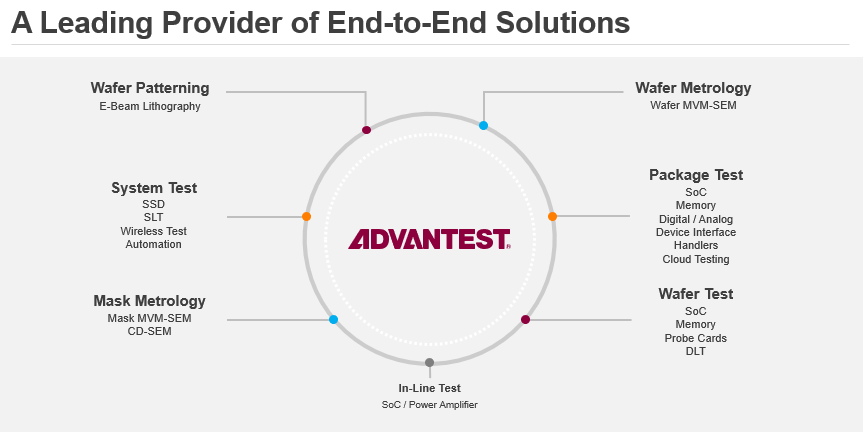

基于电光采样的时域反射计(EOS-TDR)在有效检测芯片封装中的轻微缺陷方面具有巨大的前景,无论芯片内的晶体管如何运行,都可以提供对迹线结构的深入了解。如图所示,与传统基于示波器的TDR类似,EOS-TDR (ADVANTEST TS9001)将电脉冲波形注入被测器件并监测反射。然而,EOS-TDR提供的距离分辨率比传统基于示波器的TDR高为20~30倍,这使得它能精确检测由沿迹线的轻微缺陷引起的微小波形偏差。此外,与传统TDR产生的阶梯波相比,EOS-TDR生成的窄脉冲波具有更好的缺陷定位识别能力。

EOS-TDR提供了检测轻微缺陷的能力,这些轻微缺陷以前只能通过在极端条件下进行的功能测试来识别。有了EOS-TDR,这些缺陷现在可以在正常环境温度的断电状态下测到。例如,相比于功能测试只能识别70°C下的部分开路,EOS-TDR可以在室温下鉴别出这个会导致高温开路的轻微缺陷的存在[5]。同样,功能测试需要在135°C 才能发现的通孔裂纹,EOS-TDR也可以在室温下通过反射波行的偏差来发现。一般来说,这些波形偏差是由缺陷单元中的缺陷和良好单元中的样本间差异z造成的。为了利用EOS-TDR在众多良好波形中有效识别轻微缺陷,必须全面了解不同轻微缺陷场景导致的波形偏差,并进行统计分析以识别异常值。

在这项工作中,我们进行了初步研究,以便通过分析EOS-TDR波形能够检测轻微缺陷。该研究包括两个主要步骤。首先,生成代表典型轻微缺陷的电路模型,并分析相应的EOS-TDR响应。这样可以更深入地了解与轻微缺陷相关的波形特性。其次,探索了一种基于互相关的离群波形检测方案来识别一般轻微缺陷。通过仿真和测量验证了该方案的有效性,保证了其检测轻微缺陷的可靠性。

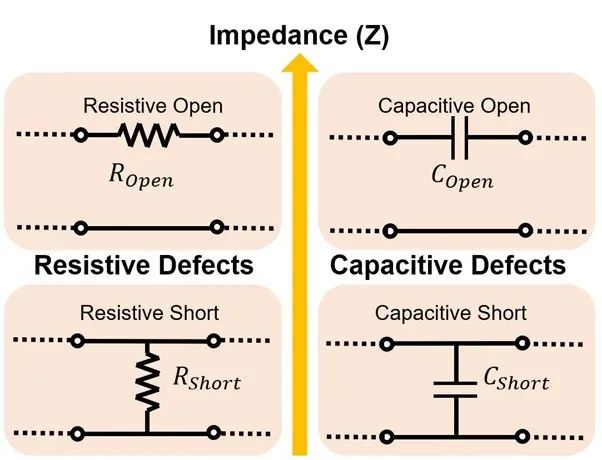

2.封装轻微缺陷建模

图中展示了芯片封装中的几种典型轻微缺陷,包括电阻性缺陷和电容性缺陷。电阻性和电容性缺陷都会增加或减少负载阻抗。如果存在电阻性开路或电容性开路缺陷,负载阻抗会较高;如果有电阻性短路或电容性短路缺陷,负载阻抗会较低。

3.离群TDR波形检测方案

由于轻微缺陷导致的EOS-TDR波形偏差是双重的:与阻抗相关或与位置相关。以脉冲反射为例,脉冲幅度与阻抗相关,而脉冲时间与位置相关。图5显示了基于互相关的轻微缺陷检测方案,该方案包括3个步骤:时间窗口识别、特征提取和Hoteling的T2-test。与广泛使用的主成分分析[7]相比,互相关提取的特征对幅度和时间变化更加敏感。

4.电路仿真

显示了EOS-TDR测量下倒装BGA封装芯片样品中选定信号引脚的布局和电路图。脉冲信号通过射频探针注BGA球,然后沿着基板中的迹线传播并到达模具。如果芯片-基板界面的阻抗不完全匹配,则脉冲信号将被部分反射。如果大多数晶片焊垫都带有典型去耦电容在0.2~2pF范围内的ESD保护[8],则负脉冲将被EOS-TDR系统反射并检测到。封装中的轻微开路缺陷可能发生在沿迹线的任何地方,例如球、通孔、凸块。将所提出的方法的验证被简化为所选信号引脚P1和P2的两个位置,分别代表球-基板接口和基板模具接口。

登录

登录