ISSCC(International Solid-State Circuits Conference)国际固态电路会议,是世界学术界和企业界公认的集成电路设计领域最高级别会议,被认为是集成电路设计领域的“世界奥林匹克大会”。会议为从事 IC 设计和应用前沿工作的工程师搭建了一个独特的展示平台,并为其提供了与领先的行业专家交流学习的机会。

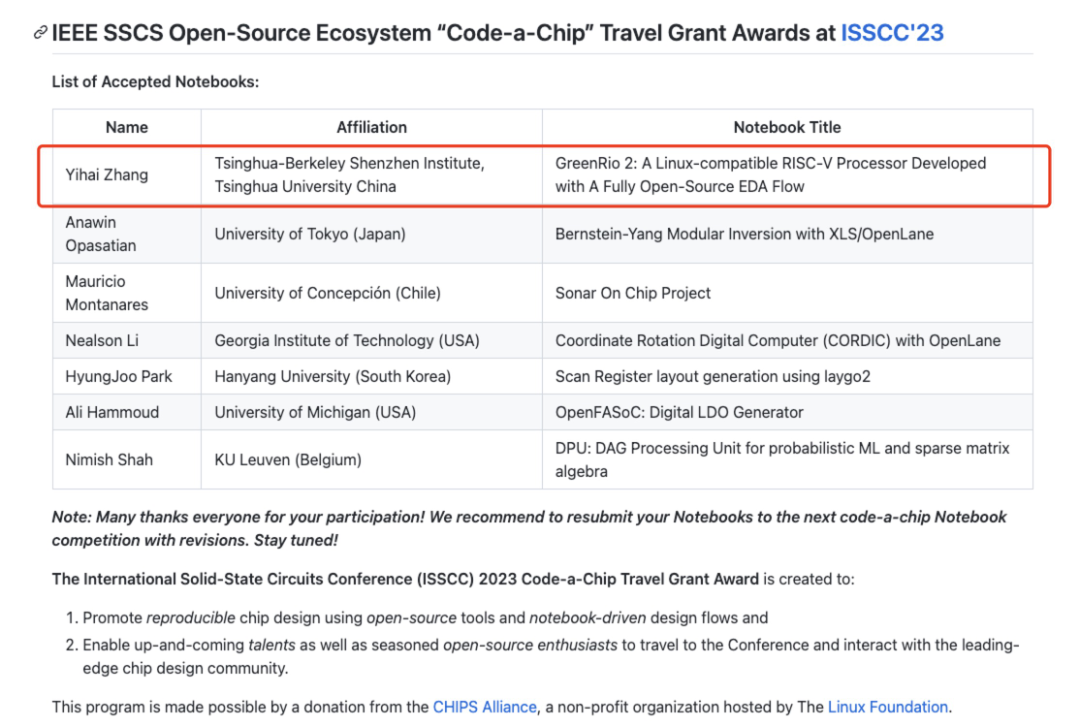

首届“Code-a-Chip”比赛由 CHIPS Alliance 和 Google 赞助支持。CHIPS Alliance是一个由Google, Microsoft, Intel, Nvidia, Infinion, 阿里巴巴, Berkeley, Stanford等行业领头企业及高等学府共同组建,以开发和管理高质量开源硬件代码(IP 核)、互连 IP(物理和逻辑协议)以及用于设计、验证等的开源软件开发工具的组织。

张乙海(Yihai Zhang),RISC-V 国际开源(RIOS)实验室研一学生,在由ISSCC会议举办的首届”Code-A-Chip”比赛中,凭借参赛项目「GreenRio v2.0」获得第一名的殊荣!他在ISSCC 2023峰会的学生研究展示环节中对此项目进行了研究成果阐述及海报展示。

参赛项目

GreenRio v2.0为RIOS实验室开源项目,由开源项目GreenRio v1.0迭代而来,旨在构建从RTL到芯片版图的全开源流程设计,并探究开源EDA软件能够实现的微处理器架构的复杂度上限,最后能够成为从概念验证原型到学术研究平台和工业生产的开源处理器。

GreenRio v2.0 Architecture

GreenRio v1.0已经过OpenMPW-7流片测试验证并且是OpenMPW-7与OpenEDA流程中目前最复杂的设计。迭代后的GreenRio v2.0是一个开源,超标量以及Linux兼容的微处理器设计,在开源结构,开源验证和开源后端流程中实现了技术突破。

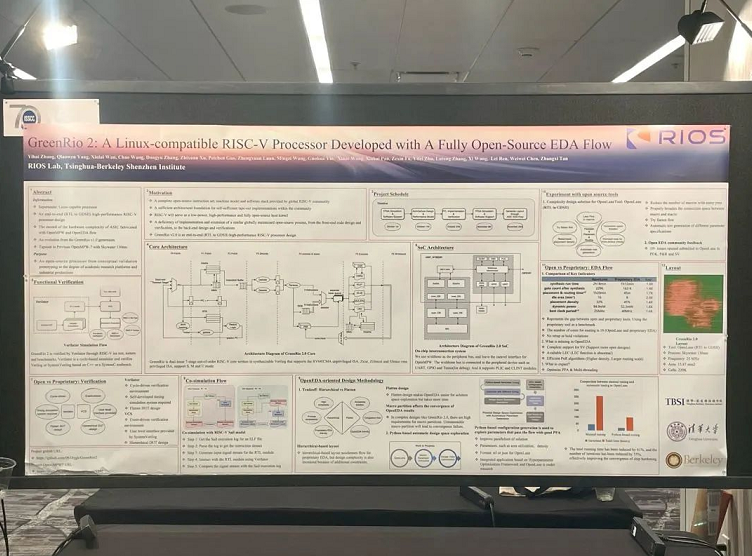

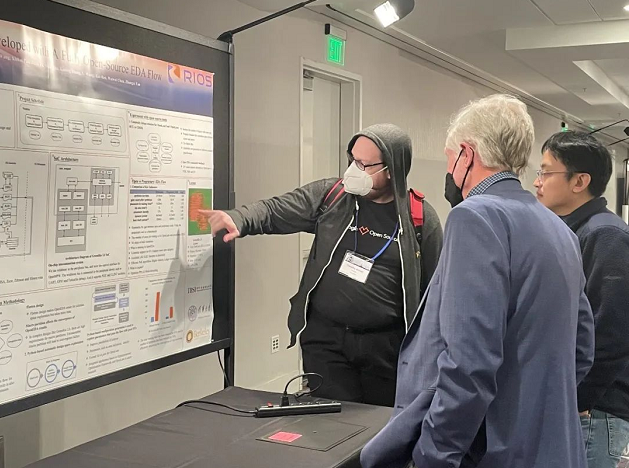

会议现场,我们就GreenRio v2.0进行了项目演示,阐述了该项目的研究重点和设计方法。

在GreenRio v2.0的设计方法学上,我们设计了基于C++的性能模型,基于形式化语言的功能协同仿真。在ASIC后端流程中,我们基于层次化的后端理念,设计了基于Python的自动化设计收敛的探索模型,对比基于人工的后端流程,设计时间减少了60%。并给予实践经验,在SystemVerilog支持,LEC支持以及PnR优化策略上给予开源EDA软件方反馈,力求缩小开源EDA软件与专用EDA软件的差距,打造更完善的开源生态。

海报展示

项目演示结束后,GreenRio v2.0受到了业界学者和专家们的一致关注,纷纷前往海报区进行深度咨询和技术交流。

Rob Mains, CHIPS Alliance负责人

Tim Ansell, Google OpenPDK/EDA负责人

谭章熹 博士, RIOS Co-director

登录

登录