西安电子科技大学模拟集成电路重点实验室赵潇腾、朱樟明团队在高能效高速数据接口芯片方向取得重要进展。团队基于65nm CMOS工艺提出了一款高能效、小面积、同时具有带内带外噪声抑制能力的9–21 Gb/s倍频亚采样型(FXSS)时钟与数据恢复(CDR)电路,采用无电感架构,并内嵌1:3解复用器,有效降低了高速串行接口中时钟恢复、数据重定时和片上时钟分布的面积与功耗开销,适用于数据中心多通道SerDes接口、超短距芯粒互连等应用场景,相关成果发表在《IEEE Journal of Solid-State Circuits》(JSSC)2026年第5期,论文题目为"A 0.0006-mm², 0.13-pJ/bit, 9–21-Gb/s Sub-Sampling CDR With Inverter-Based Frequency Multiplier and Embedded 1:3 DEMUX in 65-nm CMOS"(2026,vol. 61, no. 5, pp. 2059-2072)。论文第一作者为西安电子科技大学董志成,通讯作者为西安电子科技大学国家青年人才赵潇腾。

论文链接

https://ieeexplore.ieee.org/document/11152346/

(查看全文可点击文末“阅读原文”)

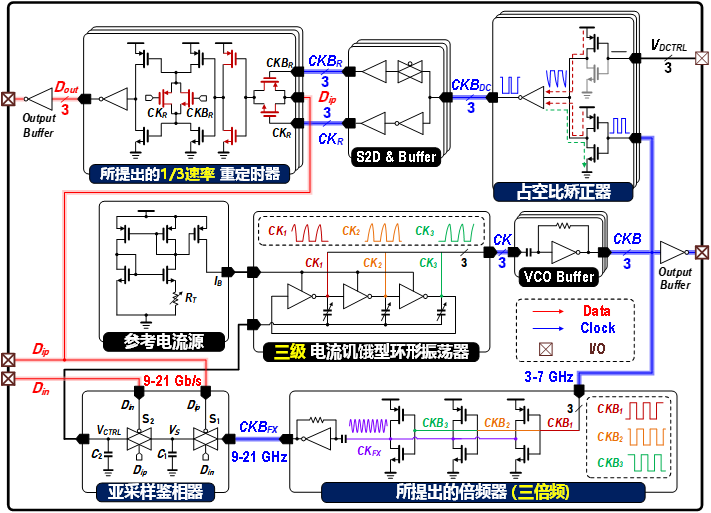

该工作基于所提出的FXSS CDR架构,通过在反馈路径中引入反相器型频率倍乘器,使环形压控振荡器和传输门型重定时器仅需工作在三分之一速率,从而缓解传统全速率无电感CDR中振荡器和重定时器的速度瓶颈。与此同时,所采用的主从式亚采样鉴相器能够支持低摆幅全速率倍频时钟,并结合约200MHz的环路带宽,可有效抑制带内输入噪声和带外环形振荡器噪声。进一步引入紧凑的反相器型占空比校正电路,实现精细的重定时偏斜校准,改善了系统在高速数据恢复中的抖动容限和误码性能。

图1 所提出的FXSS CDR架构

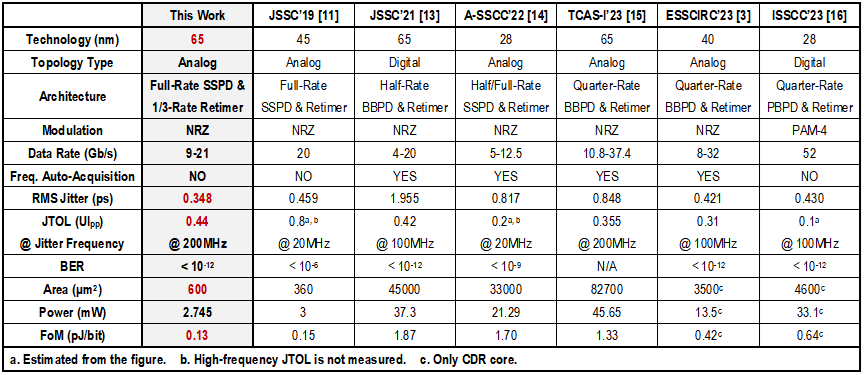

基于65nm CMOS工艺,该CDR核心面积仅为0.0006 mm²,在21 Gb/s下功耗为 2.75 mW,能效达到0.13 pJ/bit,并实现348.2 fsrms的积分抖动和0.44 UIpp@200 MHz 的抖动容限。该工作在已报道无电感CDR中实现了近年最优的能效、世界领先的面积效率与抖动等综合性能,为高密度、多通道高速数据接口提供了高能效、紧凑的时钟数据恢复解决方案。

表1 该工作与无电感CDR的性能对比

论文信息

Zhicheng Dong, Xiaoteng Zhao, Zekai Yang, Xianting Su, Haolin Han, Feng Bu, Depeng Sun, Shubin Liu, and Zhangming Zhu. "A 0.0006-mm2, 0.13-pJ/bit, 9–21-Gb/s Sub-Sampling CDR With Inverter-Based Frequency Multiplier and Embedded 1:3 DEMUX in 65-nm CMOS,"IEEE Journal of Solid-State Circuits, vol. 61, no. 5, pp. 2059-2072, May 2026.