近日,杭州电子科技大学芯片与安全实验室(CSL)硕士生龙翔在导师夏莹杰教授指导下,与中南大学、华中科技大学等科研团队合作完成的研究成果"VerilogLAVD: LLM-Aided Pattern Generation for Verilog CWE Detection"被The 64th Annual Meeting of the Association for Computational Linguistics(ACL'26,CCF-A类会议)主会录用。实验室硕士生龙翔为论文第一作者,夏莹杰教授为通讯作者。

芯片设计语言安全漏洞检测是保障集成电路设计安全的关键环节。随着现代硬件架构日益复杂,在RTL阶段确保硬件描述语言的安全性对于构建可信硬件系统至关重要。然而,传统安全验证技术面临可扩展性受限、无法穷尽覆盖所有设计状态等问题,导致漏洞可能在芯片设计的后期才被发现,修复成本大幅提高。现有LLM方法在硬件漏洞检测中表现不佳,核心难点在于HDL固有的语义并发性,漏洞往往源于多条并发执行语句的交互,而非单一顺序执行路径。

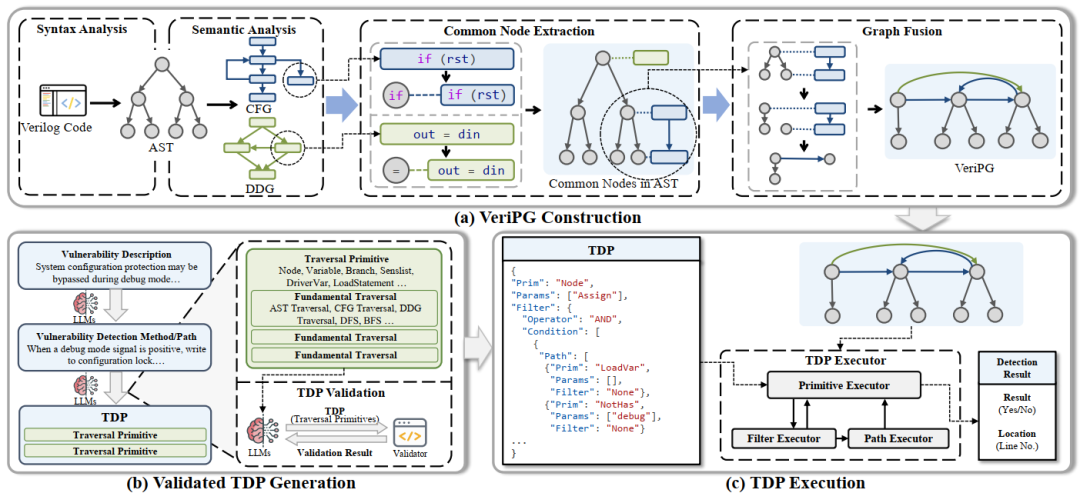

本文提出了一种LLM辅助的Verilog漏洞检测框架VerilogLAVD。首先设计了统一Verilog属性图(VeriPG),通过融合抽象语法树(AST)、控制流图(CFG)和数据依赖图(DDG)显式建模硬件并行语义;进而设计了语义验证机制,对LLM生成的可执行遍历检测模式(TDP)进行约束与过滤;最终在VeriPG上执行验证后的TDP,输出稳定的检测结果。与纯LLM方法相比,本文方案F1分数提升了0.31,并成功在开源硬件设计仓库中发现真实安全漏洞。

ACL是中国计算机学会(CCF)推荐的A类国际会议,是自然语言处理与计算语言学领域国际顶级会议,具有极高的学术影响力。