双倍数据速率同步动态随机存取存储器(DDR SDRAM 或直接称为 DRAM)技术,如今已成为几乎所有应用(从高性能计算到注重功耗/面积的移动应用)中的事实存储器。

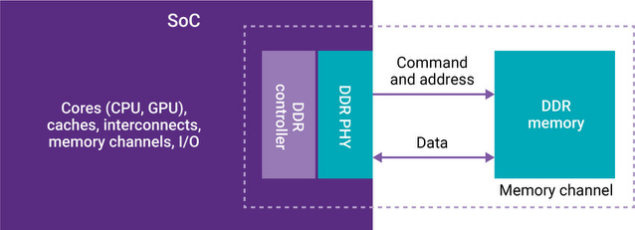

JEDEC(固态技术协会)定义并制定了 DRAM 类 DDR 标准(DDR 标准:DDR、DDR2/3/4/5、移动 DDR:LPDDR2/3/4/5、图形 DDR:GDDR3/4/5/6 和高带宽 DRAM:HBM、HBM2/2E/3),以此能够指导设计人员精确地满足其存储器要求。图 1显示了片上系统 (SoC) 中存储器通道的高级框图。高性能 SoC 通常具有多个存储器通道。图示显示的简化 DDR 存储器可以是上述任何 DDR 类别的 DRAM 存储器。

图 1:SoC 中的存储器通道框图

为了确保存储器通道链路的可靠稳定,通常需要训练内存接口。而DDR内存接口常见的训练方式有三种,其中,基于固件的训练方式优势最为明显。

训练DDR内存接口的三种方式

如图 1 所示,典型的存储器通道包含一个 DDR 控制器,连接 SoC 互连(例如 AXI 互连)接口。DDR 控制器将来自互连的传入 AXI 事务转换为 DDR 命令,并以最佳方式调度命令,进而通过 PHY 和存储器通道发送到 DDR 存储器。

DDR PHY 是控制器与 DDR 存储器之间的通道,是在控制器与存储器之间可靠地传输数据而不发生位错误的关键所在。为保证 DDR 通道在任务模式下的稳定性,SoC 和 DRAM 上的内存接口会在通电后被训练。

高级别训练涉及将各种模式发送到存储器,并通过更改读取 (RD) 和写入 (WR) 的时间延迟和电压来训练通道,然后在时域/电压域中找到 RD/WR 参数的最佳设置。这一方式适用于命令/地址和数据通道,具体取决于 DDR 标准和操作速度。如此,SoC 内存接口上的接收器和 DRAM 上的接收器产生的数据眼图,都可以保证任务模式器件峰值数据的正确传输。

可以通过三种不同的方式来训练 DDR 内存接口:

1、由核心 CPU 通过软件 (SW) 或固件 (FW) 进行训练;

2、由 PHY 或控制器利用专用硬件 (HW) 状态机进行训练;

3、由 PHY 利用 FW 代码进行训练。

第一种方式(即 CPU 负责通过 SW 或 FW 代码为每个通道训练内存接口)非常耗时,因为占用了宝贵的 CPU 周期来初始化其他组件。

第二种方式虽然比第一种方式快,但涉及将训练算法提交给 HW 状态机的操作。因此,在现场升级能力方面,缺少其他两个选项所具备的灵活性。此外,修复 HW 中的任何错误,通常都需要花费时间和金钱来重新设计 SoC。这个选项在支持多种 DDR 标准时也需要密集的设计,会消耗更多的面积和功率,因为每个标准可能都需要自己的自定义算法和实现方式。最后,从面积和功率的角度来看,支持复杂的数据模式可能不可行。因此,该方案通常采用的训练模式都是传统的、更简单的模式,以固定频率切换,不会对信号完整性造成太大的影响,如串扰、符号间干扰和最严重的抖动。

第三种方式,即由 PHY 利用 FW 代码进行训练,是其中最稳定的一种方法。

快速、准确、可现场升级,固件训练方式优势显著

基于固件的训练结合了前两个选项的优点,允许通过 FW 进行训练,并将训练执行完全本地化到 PHY。这样就可以并行训练 SoC 上的每个存储器通道。此外,随着存储器完成初始化,主机 CPU 可以将宝贵的周期时间花费在其他初始化活动上。而且,这种快速而准确的训练机制允许使用通用的 HW 框架进行训练,从而可以支持多种 DDR 标准。由于现在可以针对每个 DDR 标准自定义 FW,以拥有自己的训练数据模式(例如,伪随机二进制序列 23 或“PRBS23”对阵 PRBS31),在训练数据模式的复杂性方面也有灵活性。

更为重要的是,这种方法也可以现场升级,这一特性极其实用,特别是在支持新兴标准时,因为新兴标准在行业站稳脚跟之前,可能需要在 JEDEC 接受进一步的修订。新思科技在 DesignWare® DDR PHY IP 中选择这种训练方法,原因不言自明。

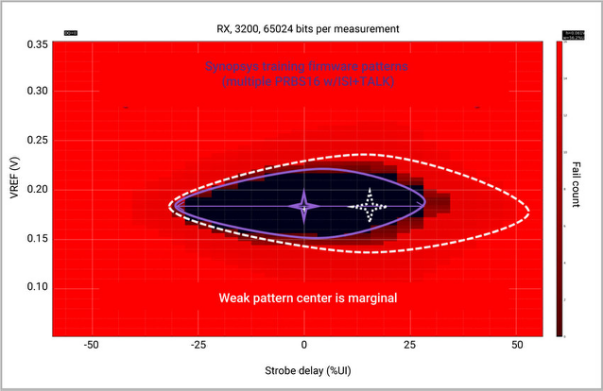

图 2 显示了第二、三个选项之间的数据眼图比较。可以看出,通过 HW 状态机进行训练时,涉及使用传统的数据模式,这可能不能完全代表任务模式流量。因此,基于 HW 状态机的训练可能会导致训练期间开眼(显示为白色),但在峰值任务模式流量期间,可能在两个方向上都不稳定。显然,基于 HW 状态机的训练设置(白星)没有集中在最坏情况下的数据眼图(紫星)中,带来了保持时间的挑战。另一方面,通过 FW使用复杂的数据模式(例如伪随机二进制序列)进行训练,通常会导致在训练过程中眼图变小(显示为紫色),从而可以优化训练后的电压和时域设置(表示为紫星),以在任务模式流量期间获得更稳定的性能。

图 2:任务模式下基于 HW 和 FW 的训练结果比较

总结

准确的内存接口训练是决定存储器通道稳定性的关键。尽管可以通过三种方式来训练内存接口,但是使用固件进行 PHY 训练是快速、准确和可现场升级的最佳训练机制。新思科技在所有需要复杂训练的 DesignWare DDR PHY IP 中都采用了这种训练方法,可以帮助客户成功实现其内存接口的性能目标。

(校对/范蓉)

登录

登录